Product Summary

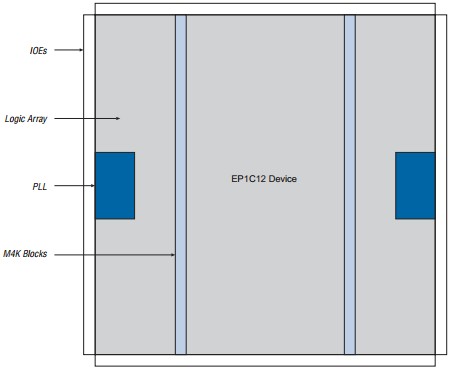

The EP1C3T100I7N is a cyclone device which belongs to cyclone FPGA family. Cyclone devices contain a two-dimensional row- and column-based architecture to implement custom logic. Column and row interconnects of varying speeds provide signal interconnects between LABs and embedded memory blocks. The Cyclone(TM) field programmable gate array family is based on a 1.5-V, 0.13-μm, all-layer copper SRAM process, with densities up to 20,060 logic elements (LEs) and up to 288 Kbits of RAM. With features like phaselocked loops (PLLs) for clocking and a dedicated double data rate (DDR) interface to meet DDR SDRAM and fast cycle RAM (FCRAM) memory requirements, Cyclone devices are a cost-effective solution for data-path applications. Cyclone devices support various I/O standards, including LVDS at data rates up to 311 megabits per second (Mbps) and 66-MHz, 32-bit peripheral component interconnect (PCI), for interfacing with and supporting ASSP and ASIC devices. Altera also offers new low-cost serial configuration devices to configure Cyclone devices.

Parametrics

EP1C3T100I7N absolute maximum ratings: (1)Supply voltage: –0.5 to 2.4 V; (2)DC input voltage: –0.5 to 4.6 V; (3)DC output current, per pin: –25 to 25 mA; (4)Storage temperature: –65 to 150°C; (5)Ambient temperature: –65 to 135°C; (6)Junction temperature: 135°C.

Features

EP1C3T100I7N features: (1)2,910 to 20,060 LEs; (2)Up to 294,912 RAM bits (36,864 bytes); (3)Supports configuration through low-cost serial configuration device; (4)Support for LVTTL, LVCMOS, SSTL-2, and SSTL-3 I/O standards; (5)Support for 66-MHz, 32-bit PCI standard; (6)Low speed (311 Mbps) LVDS I/O support; (7)Up to two PLLs per device provide clock multiplication and phase ; (8)shifting; (9)Up to eight global clock lines with six clock resources available per ; (10)logic array block (LAB) row; (11)Support for external memory, including DDR SDRAM (133 MHz), ; (12)FCRAM, and single data rate (SDR) SDRAM; (13)Support for multiple intellectual property (IP) cores.

Diagrams

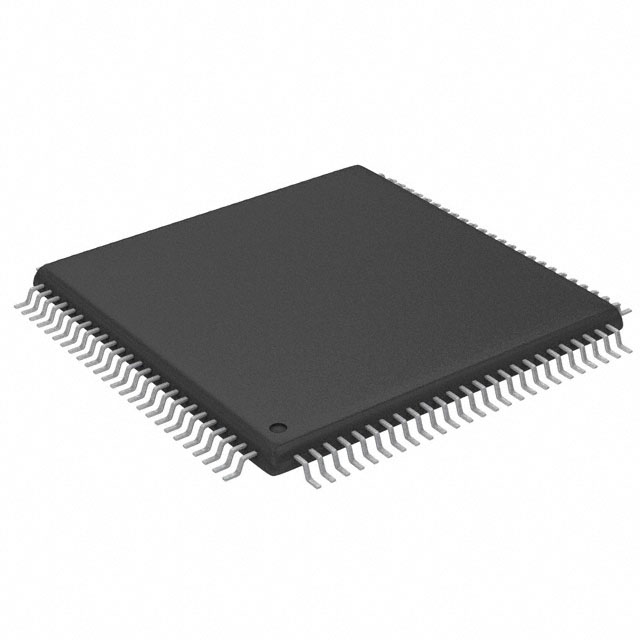

| Image | Part No | Mfg | Description |  |

Pricing (USD) |

Quantity | ||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|

|

EP1C3T100I7N |

|

IC CYCLONE FPGA 2910 LE 100-TQFP |

Data Sheet |

|

|

||||||

| Image | Part No | Mfg | Description |  |

Pricing (USD) |

Quantity | ||||||

|

EP1C12 |

Other |

|

Data Sheet |

Negotiable |

|

||||||

|

EP1C12F256C6 |

|

IC CYCLONE FPGA 12K LE 256-FBGA |

Data Sheet |

|

|

||||||

|

EP1C12F256C6N |

|

IC CYCLONE FPGA 12K LE 256-FBGA |

Data Sheet |

|

|

||||||

|

EP1C12F256C7 |

|

IC CYCLONE FPGA 12K LE 256-FBGA |

Data Sheet |

|

|

||||||

|

EP1C12F256C7N |

|

IC CYCLONE FPGA 12K LE 256-FBGA |

Data Sheet |

|

|

||||||

|

EP1C12F256C8 |

|

IC CYCLONE FPGA 12K LE 256-FBGA |

Data Sheet |

|

|

||||||

(China (Mainland))

(China (Mainland))